## Sonnet EM Simulation of Printed Baluns Using PCB Data Extraction

# Claudio M. Montiel<sup>1</sup>

<sup>1</sup> Department of Electrical Engineering and Computer Science Texas A&M University - Kingsville, Kingsville, TX 78363, USA claudio.montiel@tamuk.edu

**Abstract:** This paper describes the validation of printed circuit board (PCB) microstrip baluns from the files sent to board fabrication facility. The baluns' geometries were extracted from AutoCAD DXF and Gerber files and verified using the Sonnet EM simulator. The baluns were originally designed using transmission line models. The geometries were based on the 180° hybrid junction, with one port removed to form a T-junction combiner with a phase shift. Because the baluns were modified during layout, the gerbers were imported into the EM simulator for verification.

Keywords: Baluns, Microstrip, 180° Hybrid, T-Junction, DXF, Gerber Extraction

### 1. Introduction

Testing integrated circuits continues to be a costly endeavor and consequently cost reduction is an important goal for semiconductor manufacturers [1-3]. These cost reduction pressures have spread to envelope all types of RF and wireless products and all stages of production [4-5]. The project described in this paper involved the development of a low-cost high-volume ATE solution for two radio frequency integrated circuits (RFICs) designed for broadband wireless access.

The devices share the same footprint and pin-out as well as the same programming protocols. Although they are both designed as components in the receiver chain of broadband wireless access systems, the low-band (LB) device is designed for the 2.5GHz band, while the high-band (HB) device is for use in the 3.5 GHz band. The devices are part of radio chipsets and are designed to function as the second down-converter and to provide the LO signal for the first down-converter. The devices under test (DUTs) share extensive internal circuitry and are essentially identical except for the LO synthesizer frequency ranges.

The RFICs were first released using a low-volume test solution. After initial product demand increased, higher volumes and lower costs became imperative. As a result, the products were transitioned to high-volume automated test equipment (ATE) for increased throughput and test coverage, while providing reduced production costs. Since increased capabilities were available, a high-performance handler interface board (HIB) was designed with dual switched baluns.

The balun designs are based on the widely used rat-race hybrid ring coupler whose characteristics are well understood [6-7]. When used as a power combiner, the input signals are applied at Ports 2 and 3. Ports 1 and 4 are the difference and sum outputs, respectively. In our situation, because the input signals

are completely out of phase, the desired output is at Port 1 and Port 4 has no signal. The hybrid ring can then be cut open and Port 4 removed. The baluns then become T-junction power combiners. The ring does not have to be circular as long as the wavelength or phase relationships between the ports are maintained.

#### 2. Low-Volume Test Board Balun

The original test solution used bench instrumentation under LabView control. To reduce cost and simplify testing, the low-volume test board had a wideband balun at the LO output for differential to single-ended conversion. Most modern communication systems use differential or balanced topologies for improving unwanted or spurious mixer by-products, noise immunity, gain, and linearity. The balun is required for interfacing with the single-ended spectrum analyzer in the test setup [8].

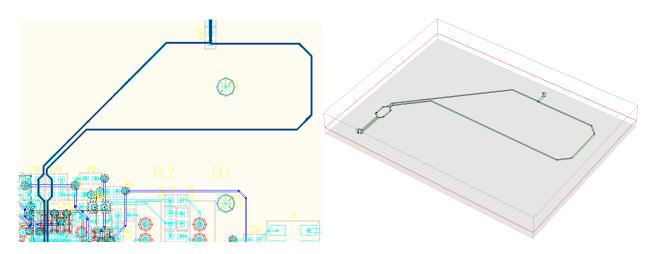

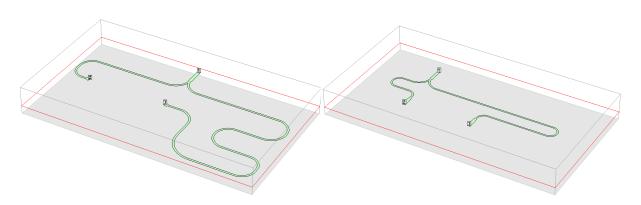

The balun was designed using transmission line models. The simulations showed that the best measurement match occurred at 1525 and 2970 MHz, but that the amplitude and phase balance would be slightly off at those frequencies. The low-volume manual test board was built using FR-4, with a dielectric constant of 4.34 at 1 GHz, and one ounce copper. The RF layers were 10 mils thick. The original hybrid balun was constructed with arm lengths of 1510 mils and 3010 mils for the  $\lambda/4$  and  $3/4 \lambda$  arms, respectively. The 71  $\Omega$  lines were 10 mils wide. The balun was extracted from the layout file and imported into Sonnet. Figure 1 shows the balun layout and the imported geometry.

Fig. 1. The low-volume board balun layout (left) and imported (right) geometries.

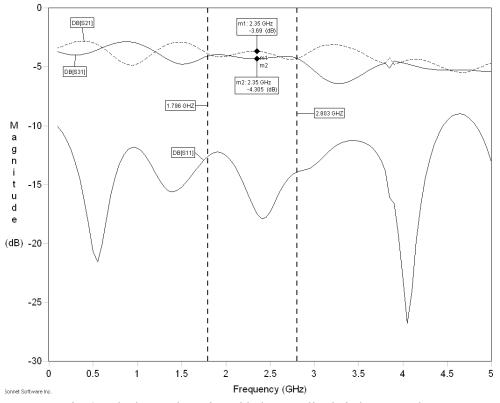

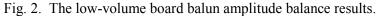

The Sonnet EM simulation showed that an input return loss of better than 10 dB for an extremely wideband from 100 MHz to 4.3GHz. The best amplitude match between ports 2 and 3 occurs at a very respectable range from 1.8 - 2.8 GHz, with a maximum amplitude imbalance of only 0.6 dB, as shown in Fig. 2. The phase imbalance for the same frequency ranged between -40° and 48°. This is shown in Fig. 3. The large variation in phase did not allow of accurate determination of the LO output power for neither the low-band nor the high-band device. This required extensive correlation experiments to produce an acceptable test solution.

Fig. 3. The low-volume board balun phase imbalance results.

#### 3. High-Volume ATE Load Board Baluns

The ATE load board was designed with separate narrowband baluns to improve the LO output singleended power measurement. This decision required switching two different baluns. The baluns are switched using small form factor RF relays. The low-band balun was designed to operate from 1700 to 2400 MHz; the high-band balun from 2400 to 3550 MHz. Because of layout considerations, the baluns were manufactured on opposite sides of the load board. The RF layers used Nelco N4000 13SI, 10 mils thick, with one ounce copper. The baluns were implemented with meandered lines to minimize their footprint. The final geometry of the baluns is shown in Fig. 4.

Fig. 4. The ATE low-band (left) and high-band (right) balun layouts.

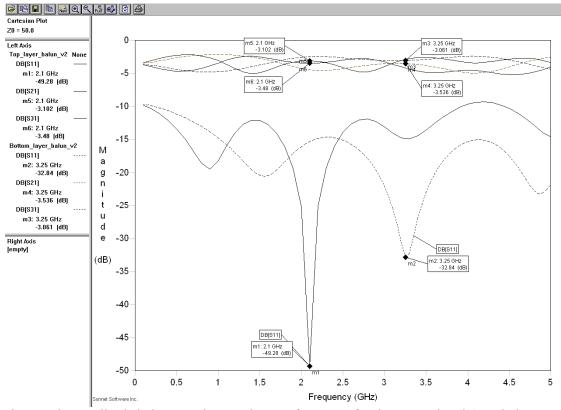

The narrowband baluns perform much better than the one used in the low-volume test board. This allowed for more precise power output measurements and reduced correlation factors in the final test solution. The amplitude balance for both baluns is shown in Fig. 5. Note that by re-centering the balun at the geometric mean of the desired frequency ranges, only a modest improvement in amplitude balance is achieved. The good return loss of better than 10 dB at Port 1 is maintained throughout the frequency range of interest.

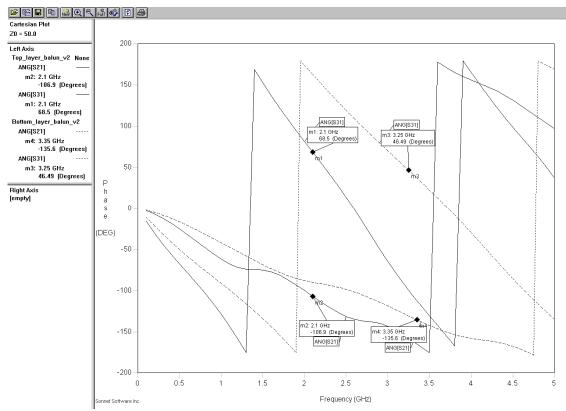

The phase balance, however, is greatly improved. This can be clearly seen in Fig. 6. At the best match frequencies of 2.1 and 3.25 GHz, the phase mismatch is reduced to  $5^{\circ}$  and  $2^{\circ}$ , respectively. For the entire band of interest, each balun phase imbalance is less than  $10^{\circ}$ .

The baluns were subsequently measured using a vector network analyzer. The results obtained showed that, for the bands of interest, both baluns performed well and increased the range of frequencies of acceptable performance. The measurements were made with 50  $\Omega$  terminations on each of the balanced arms. Other performance characteristics were verified and found to be acceptable. It was also determined that the ATE paths introduced unwanted losses that were de-embedded using the technique discussed in [9].

Fig. 5. The amplitude balance and return loss performance for the narrowband ATE baluns.

Fig. 6. The phase balance performance for the narrowband ATE baluns.

## 4. Conclusion

In this paper, the design of two PCB baluns for a high-volume ATE load board for two devices with a differential LO output were presented. The experimental results showed slight differences from the simulation results, which stemmed from the vias, RF relays, cables, and connectors required by the ATE solution. These issues of interconnect modeling and of accounting for parasitic effects is not trivial, especially for high frequency circuits, and is a matter of continued interest among researchers [10].

The results confirmed that switching between two narrowband baluns provided superior performance, especially in terms of phase balance. This allowed for better correlation for the LO power output measurement between the ATE results and the dedicated evaluation boards. This resulted in a successful high-throughput ATE solution that reduced production costs and increased test coverage.

### Acknowledgement

The author wishes to acknowledge Mr. David Briggs, Mr. Nicolas Salamina, and Mr. Chris Pearson, of Texas Instruments, Inc., for the opportunity to participate in this project, Dr. Sung-Won Park, of Texas A&M University – Kingsville, and Mr. Jim Merrill, and Mr. Greg Alton of Sonnet Software for their support and valuable discussions.

#### References

- S. Sundar, B. C. Kim, T. Byrd, F. Toledo, S. Wokhlu, E. Beskar, R. Rousselin, D. Cotton, and G. Kendall, "Low Cost Automatic Mixed-Signal Board Test Using IEEE 1149.4," *IEEE International Test Conference*, pp.1-9, 21-26 Oct. 2007.

- [2] T. P. Warwick, "What a Device Interface Board Really Costs: An Evaluation of Technical Considerations for Testing Products Operating in the Gigabit Region," *Proc. International Test Conference*, pp. 555-564, 2002.

- [3] S. S. Akbay, A. Halder, A. Chatterjee, and D. Keezer, "Low-Cost Test of Embedded RF/Analog/Mixed-Signal Circuits in SOPs," *IEEE Trans. on Advanced Packaging*, vol.27, no.2, pp. 352-363, May 2004.

- [4] G. Srinivasan, F. Taenzler, and A. Chatterjee, "Online RF Checkers for Diagnosing Multi-Gigahertz Automatic Test Boards on Low Cost ATE Platforms," *Proc. Design, Automation and Test in Europe (DATE '06)*, vol.1, pp.1-6, 6-10 March 2006.

- [5] M. Slamani, "Testing Highly Integrated Wireless Circuits and Systems with Low Cost Tester: How to Overcome the Challenge?" *Proc. International Test Conference*, pp. 1225, 2002.

- [6] S. Belkin, "Differential Circuit Characterization with Two-Port S-Parameters," *IEEE Microwave Magazine*, vol.7, no.6, pp.86-99, Dec. 2006.

- [7] K. Chang, Microwave Ring Circuits and Antennas, John Wiley & Sons, Inc. 1996.

- [8] D. M. Pozar, *Microwave Engineering, Third Edition, John Wiley & Sons, Inc. 2005.*

- [9] C. M. Montiel, and P. S. Arora, "A Dual Device Load Board with Dual Switched Printed Baluns," Proceedings of the 2010 IEEE Dallas Circuits and Systems Workshop – Design Automation, Methodologies and Manufacturability, Oct. 17-18, 2010, University of Texas at Dallas, ISBN 978-1-4244-9534-4, pp. 67-70.

- [10] C. M. Albina, and G. Hackl, "Layout Parasitic Interconnections Effects on High Frequency Circuits," 6th IEEE Dallas Circuits and Systems Workshop on System-on-Chip, DCAS, pp.1-4, 15-16 Nov. 2007.