## Tutorial de Integridade de Sinais Digitais Modelos de Microstrip utilizando Sonnet

# The College of New Jersey

Agradecimento para o Engenheiro de aplicação da Sonnet's, Greg Kinnetz e para a turma do TCNJ Spring 2014 ELC 441 Digital Engineering Systems Class,

Adrian Alshuaili, Ricardo Alves, George Banis, Jason Boxer, Vincent Carbone, Stephen Coppi, Liliane DeSilva Costa, Orlando DeLaCruz, Daniel Fisher, Jordan Freedner, Pedro Gilberto Augusto, Andrew Gildea, David W. Hand, Christopher Liang, Matthew Loewenstein, joseph Maco, Alexander J. Manoski, Wayne Philip Marshall, Jared Ariel Milburn, Timothy Nugent, Jeffrey R. Owens, Kunal Saxena, Jason Robert Scott, Timothy Skinner, Christopher J. Smith, Edward R. Spencer, Nicholas Steponanko, and Yevgen Tkachuk

-- Professor Joe Jesson, jessonj@tcnj.edu 203-613-3344

## Sistemas de Engenharia Digital

#### Conteúdo

- Introdução ao Design Digital & Regras de Design

- Quais são os Sintomas de Erros de Design Digital?

- Relação entre o Domínio do Tempo e da Frequência

- Tempo de subida e Componentes de frequência de Fourier

- Onda quadrada Digital gera harmônicos ímpares

- Relação entre o Tempo Lógico de Subida e a Frequência Gerada

- Modelagem eletromagnética de Linhas de Transmissão

- Exemplo de Microstrip em PCI

- Modelo Eletromagnético de linhas de transmissão (Traços de PCI em FR4) utilizando Sonnet

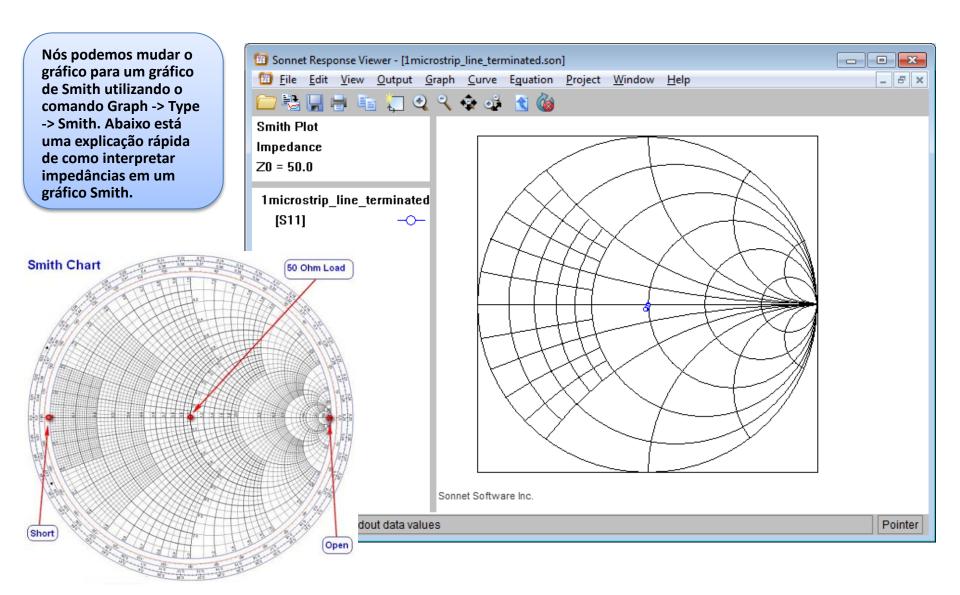

- Tutorial SONNET Finalizando o traçado da Microstrip => Construída em FR4, Gráfico S11 em dB, Plot VSWR, Impedância na Carta de Smith.

- Tutorial SONNET Linha Microstrip Acoplada => Plot do fim próximo do Crosstalk (NEXT) usando dB[S21] S-parametros, Densidade de corrente

- Tutorial SONNET Par diferencial de Linhas Microstrip => Extract S, Y, Z-parameter, Pi-model, N-coupled, Broadband, and Inductor Files

- Concluões de Sonnet como uma ferramenta de Simulação de Integridade de Sinais(SI) Digitais

- Ferramenta de verificação SI– Reflectometria no domínio do tempo (TDR)

- Ferramenta de verificação SI

Eye Diagram Mask

- Ferramenta de verificação SI Bit Error Rate Tester (BERT)

- Ferramentas de Verificação SI Analisador Vetorial de Redes(VNA)

- Conclusões do Tutorial

- Textos de Referencia:

- Hall, Hall, and McCall, High-Speed Digital System Design, John Wiley & Sons Inc., 2000

- Johnson and Graham, High Speed Signal Propagation, Prentice Hall, 2003

### Introdução ao Design Digital & Regras de Design

# As diretrizes de design, atualmente, para Integridade de Sinal Digital com alta velocidade requer como padrão:

- Todos os traços da PCI devem ser terminados em uma impedância controlada

- Reduzir a impedância e os elementos indutivos no caminho de retorno

- Evitar Branched Routing Topology

- Projetar caminhos de aterramento e de distribuição de energia com baixa impedância

- Entender como conectores e vias mudam a impedância.

**Nota:** Engenheiros digitais iniciantes frequentemente cometem um erro não terminando a entrada - TODA entrada de alta impedância deve ser terminada caso contrário resultados intermitentes podem ocorrer e/ou uma descarga eletrostática pode danificar o Circuito Integrado.

#### Quais são os Sintomas de Erros de Design Digital?

## Os Problemas Digitais se manifestam de muitas formas e

- Bits "um" específicos são lidos como "zero" ou

- Bits "zero" transmitidos são lidos como "um"

Interferência Intersimbólica (ISI), devido à diferença de impedância

Descontinuidades de impedância

Loop de terra, dI / dt

Jitter (oscilação temporal)

Ruído Térmico

Cross Talk

Conexões ruidosas ao terra

Teste de Jitter é de crescente importância para os engenheiros, como frequências de clock do sistema estão aumentando a indução de interferência intersimbólica. Placas mães atuais possuem arquiteturas de barramento serial de alta velocidade com tempo de subida < 170 picosegundos e também a atenção da engenharia deve ser focada na adequada terminação do barramento.

## Relação entre o Domínio do Tempo e da Frequência

#### **Componetes de Frequência de Fourier**

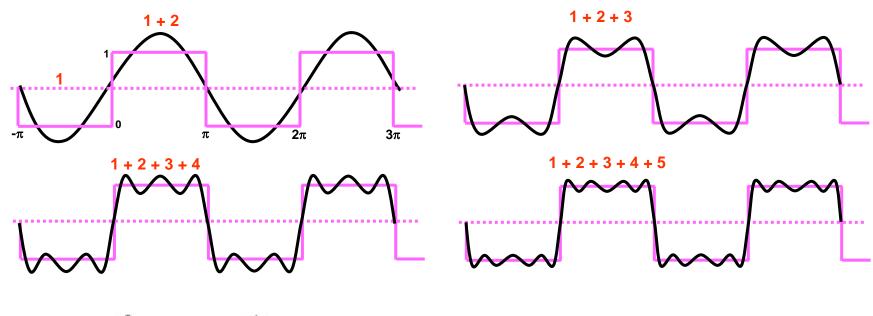

SERIES DE FOURIER — Sinais Digitais são compostos de um número infinito de funções senoidais ONDA QUADRADA: Y = 0 for  $-\pi < x < 0$  and Y = 1 for  $0 < x < \pi$ .

$$f(t) = \frac{2}{\pi} \sum_{n=1,3,5...} \frac{1}{n} \sin 2\pi n F t$$

<sup>&</sup>lt;sup>1</sup> Hall, Hall, and McCall, High-Speed Digital System Design, John Wiley & Sons Inc., 2000: 284 - 303

## Relação entre o Domínio do Tempo e da Frequência

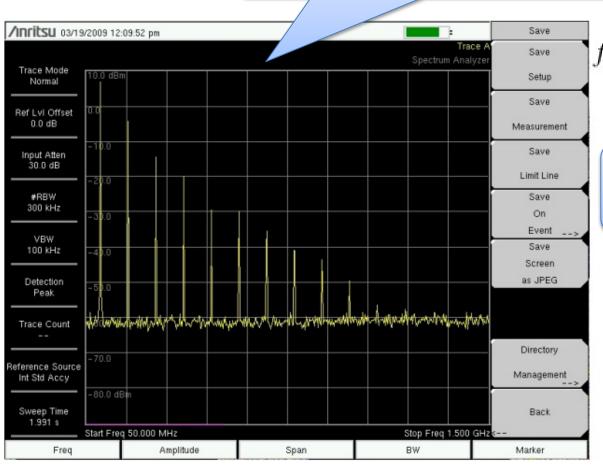

## Onda quadrada Digital gera harmônicos ímpares

Gráfico do espectro real gerado por ondas quadradas digitais que ilustra as frequência geradas por um tempo de subida de 100ps (Tr da Família Lógica ECL)

$$f(t) = \frac{2}{\pi} \sum_{n=1,3,5...} \frac{1}{n} \sin 2\pi n F t$$

<sup>1</sup> Hall, Hall, and McCall, High-Speed Digital System Design, John Wiley & Sons Inc., 2000: 85

<u>Weisstein, Eric W.</u> "Fourier Series--Square Wave." From <u>MathWorld</u>--A Wolfram Web Resource.<u>http://mathworld.wolfram.com/FourierSeriesSquareWave.html</u>

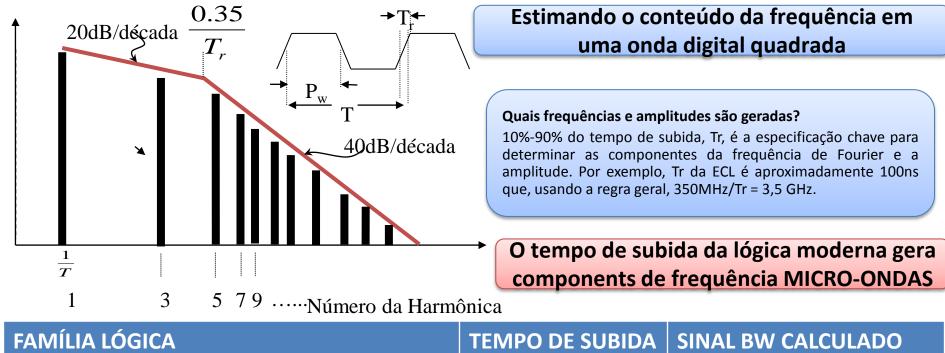

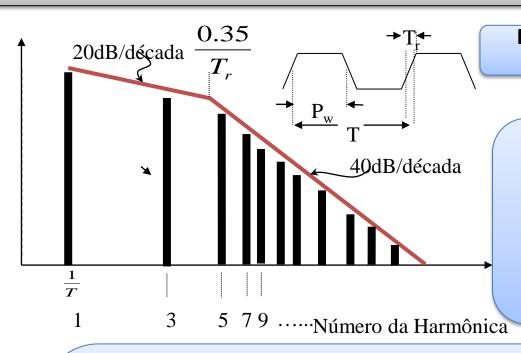

## Relação entre o Tempo Lógico de Subida e a Frequência Gerada

| $\frac{1}{T}$ 3 5 7 9Número da Harmo                    | O tempo de subida da lógica moderna gera components de frequência MICRO-ONDAS |                    |

|---------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|

| FAMÍLIA LÓGICA                                          | TEMPO DE SUBIDA                                                               | SINAL BW CALCULADO |

| Transistor Transistor-Logic (TTL)                       | 15 ns                                                                         | 24 MHz             |

| Low-Power Schottky TTL (LSTTL)                          | 2 ns                                                                          | 175 MHz            |

| Complementary Symmetry Metal Oxide Semiconductor (CMOS) | 1.5 ns                                                                        | 230 MHz            |

| Gunning Transceiver Logic (GTL)                         | 1 ns                                                                          | 350 MHz            |

| Low-Voltage Differential Signaling (LVDS)               | 400 ps                                                                        | 875 MHz            |

| Emitter-Coupled Logic (ECL)                             | 100 ps                                                                        | 3.50 GHz           |

| Gallium Arsenide Logic (GaAs)                           | 40 ps                                                                         | 8.75 GHz           |

#### Relação entre o Tempo Lógico de Subida e a Frequência Gerada

#### Estimando o conteúdo da frequência em uma onda digital quadrada

$$t_{10-90\%} = \frac{0.35}{F_{3dB}}$$

A resposta da frequência da rede digital determina o tempo de subida ou de transição resultante. A maioria do conteúdo da energia espectral, como mostrado na esquerda, estará contida abaixo de  $F_{3dB}$

#### Como podemos obter essa regra geral do tempo de subida para equação da frequência?

$$F = \frac{0.35}{Tr}$$

Pode ser derivada a partir da resposta da função degrau em um filtro & constante de tempo tau:

$$V = V_{entrada} (1 - e^{-t/\tau})$$

Definindo V=0,1 V<sub>entrada</sub> e V=0,9V<sub>entrada</sub>, calcular 10%-90% do tempo de subida em termos da constante de tempo:  $t_{10-90\%} = t_{90\%} - t_{10\%} = 2.3\tau - 0.105\tau = 2.195\tau$

A resposta em frequência de uma rede de polos é

$$F_{3dB} = \frac{1}{2\pi\tau} \to \tau = \frac{1}{2\pi F_{3dB}}$$

Substituição na resposta em degrau produz :

$$t_{10-90\%} = \frac{1.09}{\pi F_{3dB}} = \frac{0.35}{F_{3dB}}$$

## Modelagem eletromagnética de Linhas de Transmissão

- Microstrip é uma linha de transmissão frequentemente usada em projetos de placa de circuito impresso (PCI) de sinal misto.

- Há equações que são úteis para cálculos iniciais de linhas de transmissão.

- A maioria dos circuitos PCI práticos são bastante complexos e ultrapassam rapidamente as limitações das equações.

- Para uma melhor compreensão dos circuitos base de linhas de transmissão é necessário um modelo eletromagnético (EM).

- Sonnet é uma ferramenta útil para simulação EM.

#### Exemplo de Microstrip em PCI

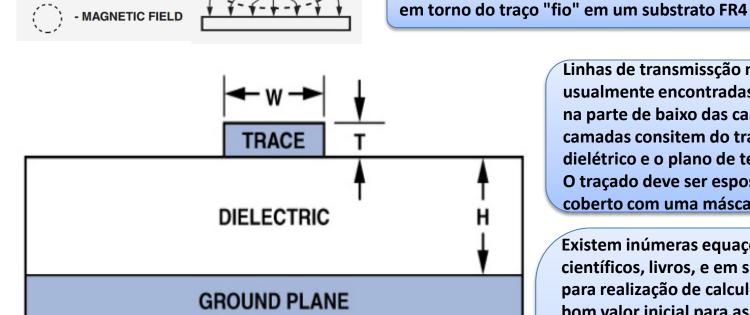

Esboço dos campos Elétricos e Magnéticos que estão

- ELECTRIC FIELD

<sup>1</sup> Hall, Hall, and McCall, High-Speed Digital System Design, John Wiley & Sons Inc., 2000: 7 - 41

Linhas de transmissção microstrip são usualmente encontradas na parte de cima e na parte de baixo das camados do PCI. Estas camadas consitem do traçado com o material dielétrico e o plano de terra mostrado abaixo. O traçado deve ser esposto para o ar acima ou coberto com uma máscara de solda.

Existem inúmeras equaçõões em artigos científicos, livros, e em software utilizados para realização de calculos, o que produz um bom valor inicial para as quantidades de linhas de transmissão. Uma das mais importantes é a impedância característica ZO. Uma decente regra de ouro a ser utilizada é a de que a largura de um traço de uma linha de transmissão microstrip deve ser aproximadamente o dobro da altura da camada do dieléctrico, de modo a produzir um Zo de 50 Ohms. Isto assumindo um material dielétrico FR-4, que tem uma Permitividade Relativa aproximada de 4.4.

#### Exemplo de Microstrip

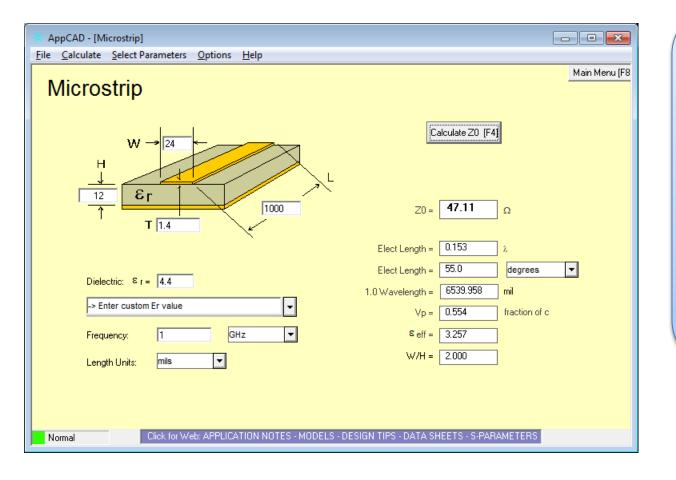

Aqui é apresentado uma imagem do programa AppCAD, que é um programa desponível gratuitamente pela Agilent/Avago. As dimensões da linha de transmissão microstrip foram selecionados de forma a computar o valor de ZO. Note que a regra de ouro (W=2\*H, para ZO de 50 Ohms) é astante precisa.

National Instruments/ AWR oferece um programa similar chamado TXLINE.

<sup>1</sup> AppCAD Utility Page: http://www.avagotech.com/pages/appcad

## Modelo Eletromagnético de linhas de transmissão utilizando Sonnet

- Sonnet utiliza o Método dos momentos, técnica de analise, para gerar dados para a estruturas de linhas de transmissão no domínio da frequência

- O particular Electromagnético solver formulation é lateralmente fechado, o que coloca o Condutor Elétrico Perfeito(CEP) protegendo as paredes ao redor do modelspace.

- É fácil de criar ou importar layouts de circuito em Sonnet.

- Existe ainda uma versão sem custo do software Sonnet (Sonnet Lite), que usaremos nos seguintes slides, para analisar algumas estruturas básicas de linha de transmissão em uma placa de circuito impresso (PCI). (A versão Sonnet Lite 14.53 é usado).

- Para mais informações, visite o site da Sonnet em www.sonnetsoftware.com.

- Por favor, consulte a documentação do Sonnet para obter uma ajuda detalhada para que se possa iniciar e configurar modelos utilizando este software.

#### **Tutorial SONNET- Finalizando o traçado da Microstrip**

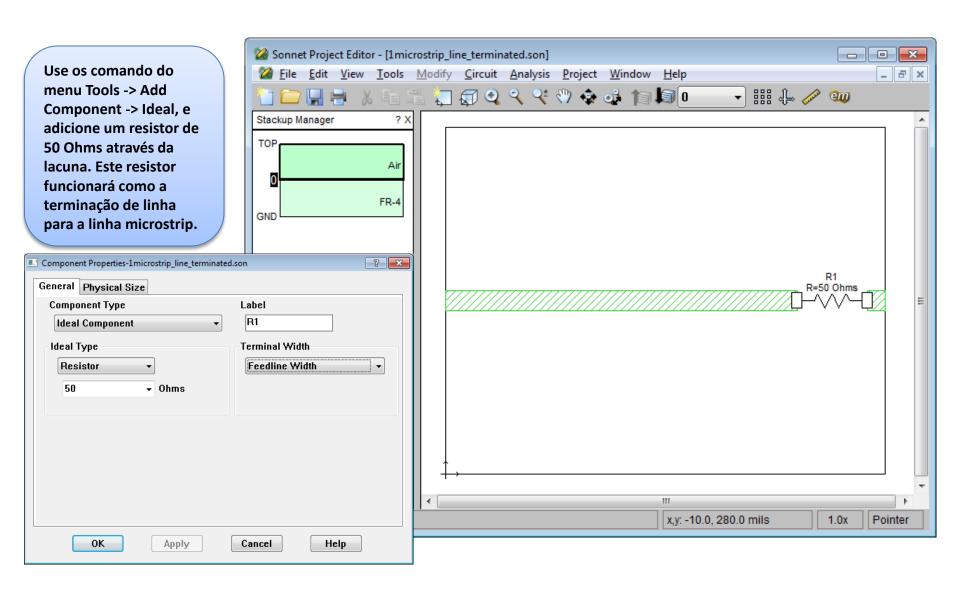

Este exercício irá demonstrar a criação de uma linha de transmissão microstrip simples terminando em um resitor ideal de 50 Ohms. Nós vamos usar as dimensões e materiais constatadas nos slides anteriores.O objetivo é familiarizar os iniciantes com o uso básico de Sonnet para projetar e analisar as linhas de transmissão para diversos fins.

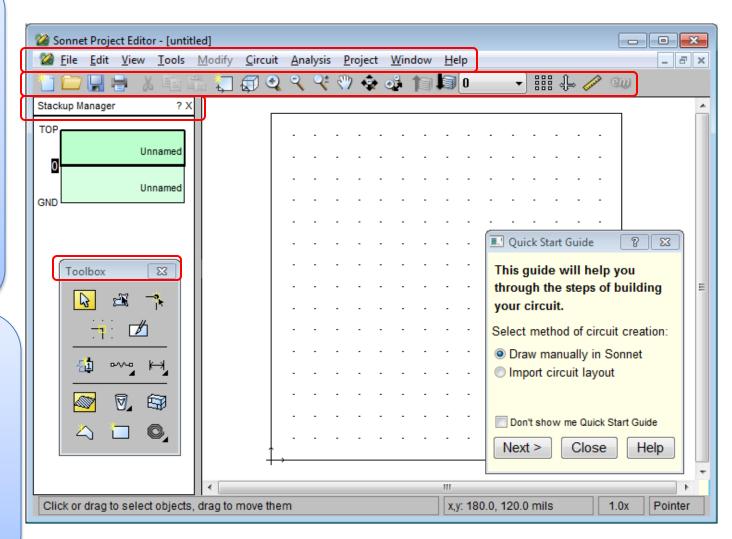

Quando você abre um novo projeto em branco uma nova janela de layout aparecerá. Há uma janela Guia de Início Rápido, que podem ajudar na criação do modelo. Para manter a interface limpa nós não utilizaremos o Guia de Início Rápido neste tutorial e ao contrário usaremos Menu Bar, Tool Bar, Tool Box, and Stackup Manager realçados.

#### **Tutorial SONNET- Completando a linha Microstrip**

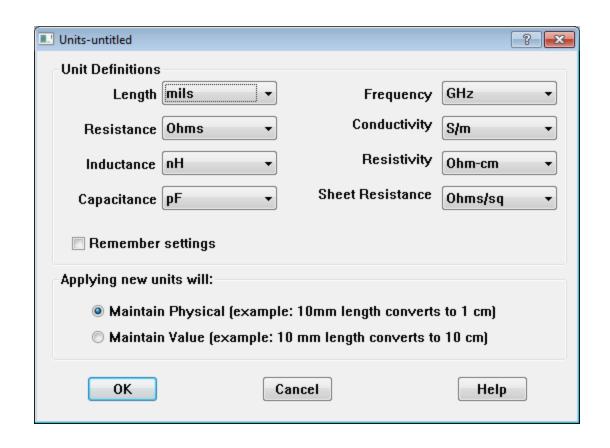

O primeiro passo é usar o comando do menu Circuit => Units e garantir que as unidades desejadas estão definidas. Vamos usar uma unidade de comprimento de mils por isso a configuração padrão está correta.

Neste ponto, é recomendavel salvar o projeto com um nome significativo. Por favor, continuem a salvar o projeto em vários pontos depois de fazer alterações.

#### **Tutorial SONNET- Completando a linha Microstrip**

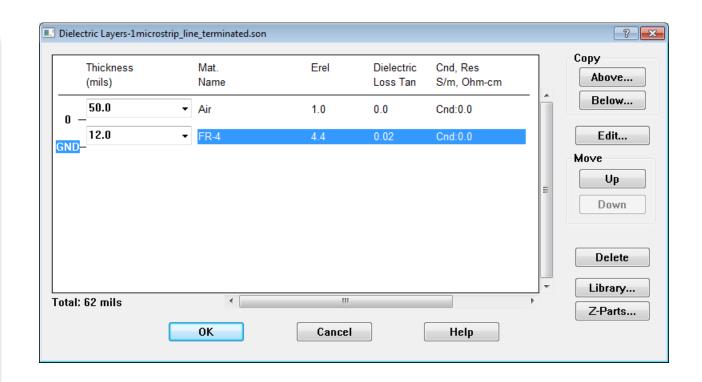

Os próximos passos não têm necessariamente de ser concluído em uma ordem específica. Vamos definir a seguir as camadas dielétricas. Esta caixa de diálogo pode ser acessado usando o comando no menu Circuit-> Dielectric Layers ou clique no botão direito do mouse sobre o Stackup Manager e selecione o mesmo comando.

Neste exemplo, é preciso inserir manualmente uma camada de ar e o material FR-4 da biblioteca. Espessuras de camadas não são armazenados na biblioteca e devem ser inseridos manualmente.

#### **Tutorial SONNET- Completando a linha Microstrip**

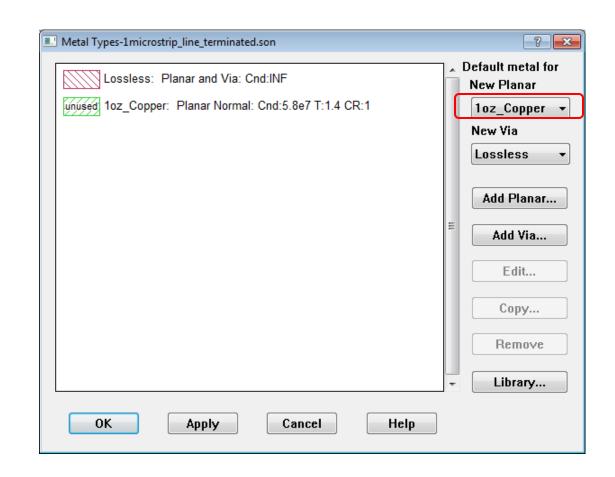

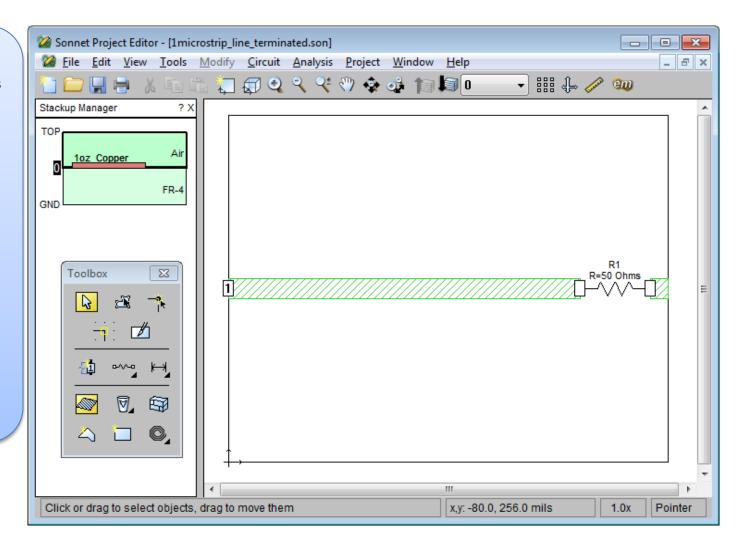

Vamos definir a seguir o tipo de metal a ser utilizado. Esta caixa de diálogo pode ser acessado usando o comando no menu Circuit-> Metal Types ou clique no botão direito do mouse sobre o Stackup Manager e selecione o mesmo comando.

Nesse exemplo, nos precisamos definir 1 onça do metal do tipo cobre (Copper metal type) usando o botão Add Planar. Assim que isso for definido, podemos ganhar tempo no futuro, atribuindo o valor de "1oz\_Copper" para um novo metal planar na lista pendente.

#### **Tutorial SONNET- Completando a linha Microstrip**

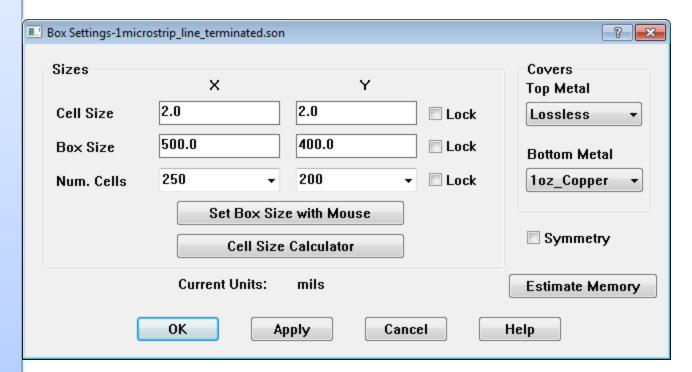

Vamos definir a seguir a caixa de análise. Isso define o tamanho X vs Y das camadas dielétricas. Esta caixa de diálogo pode ser acessado usando o comando do menu Circuit-> Box.

Neste exemplo, iremos utilizar uma caixa de tamanho de 500 x 400 mils e uma caixa de tamanho de 2 x 2 c élulas (Grade/Grid). A idéia é ter um tamanho de PCI suficientemente grande para permitirque o seu circuito utilize uma grade suficientemente fina para lidar com as dimensões que você planeja usar. O tamanho da grade é inversamente proporcional ao tamanho do modelo, por isso, deve ser cuidadosamente seleccionado.

Também podemos definir os tipos de metal da cobertura superior e inferior. Neste exemplo, vamos definir a cobertura inferior para o tipo de metal 1oz\_Copper para capturar os efeitos das perdas no plano terra do modelo.

#### **Tutorial SONNET- Completando a linha Microstrip**

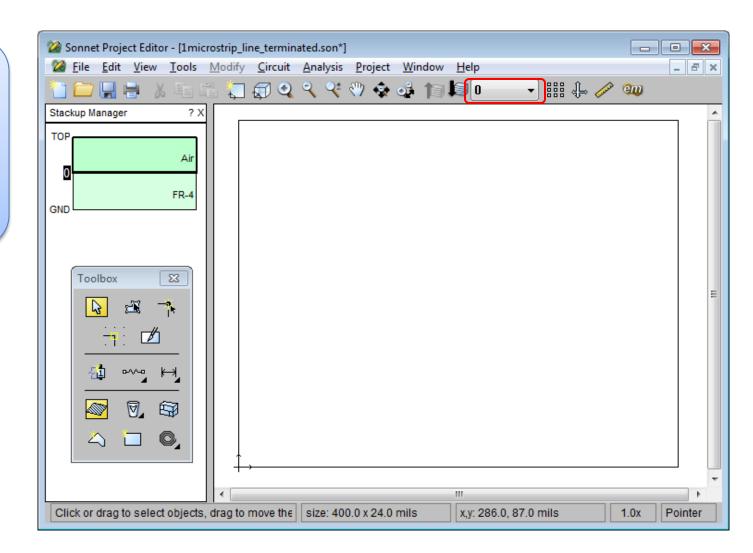

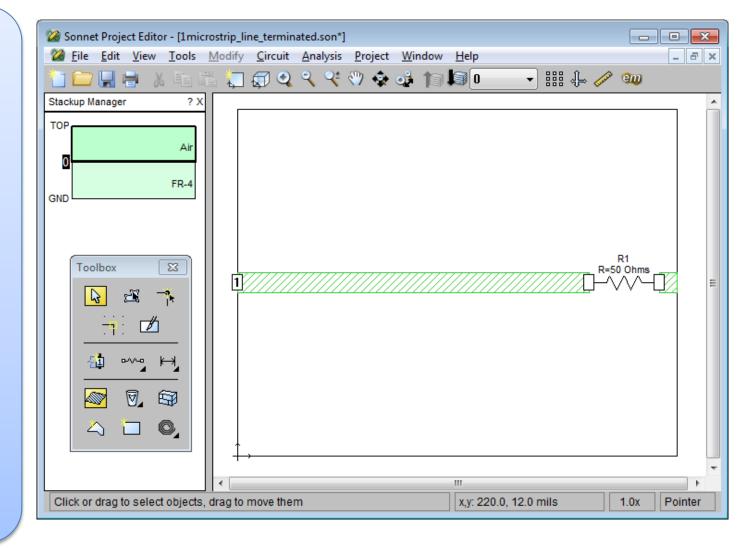

O projeto deverá ser parecido com a imagem mostrada aqui. Certifique-se de que o indicador de nível é definido como "O" e então podemos começar a adicionar os traços.

### **Tutorial SONNET- Completando a linha Microstrip**

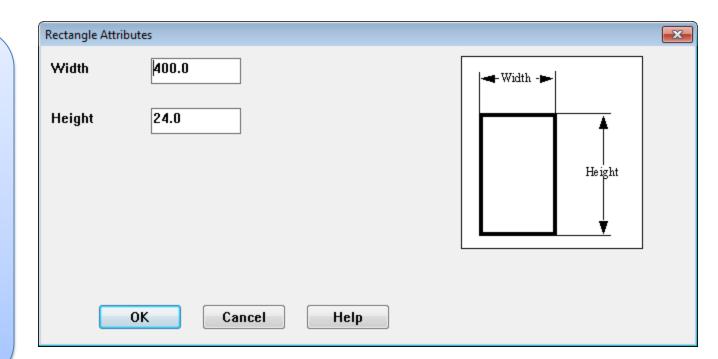

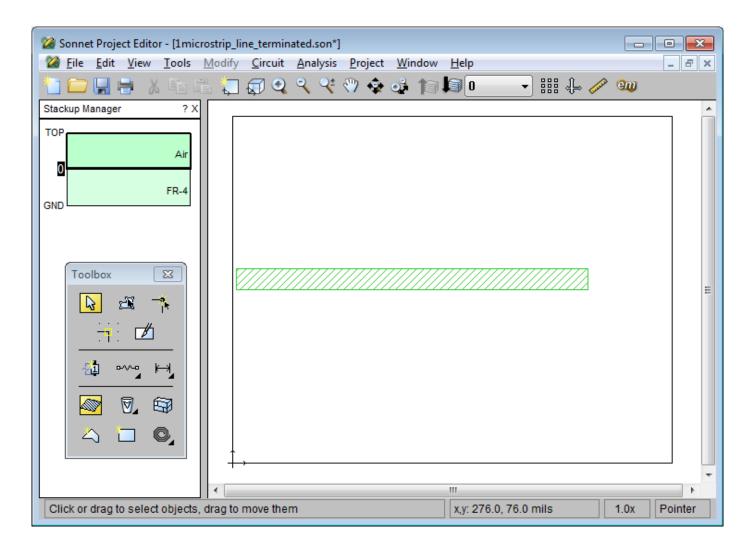

Agora estamos prontos para desenhar os traços. Existem inúmeros comandos que podem ser usados para criar layouts dentro do software Sonnet. Você também pode importar layouts existentes usando os tradutores disponíveis.Usaremos o comando Tools -> Add Metallization -> Rectangle. Definiremos os valores entre 400 e 24, como mostrado na imagem.

#### **Tutorial SONNET- Completando a linha Microstrip**

O projeto deverá ser algo no modelo da imagem mostrada aqui.

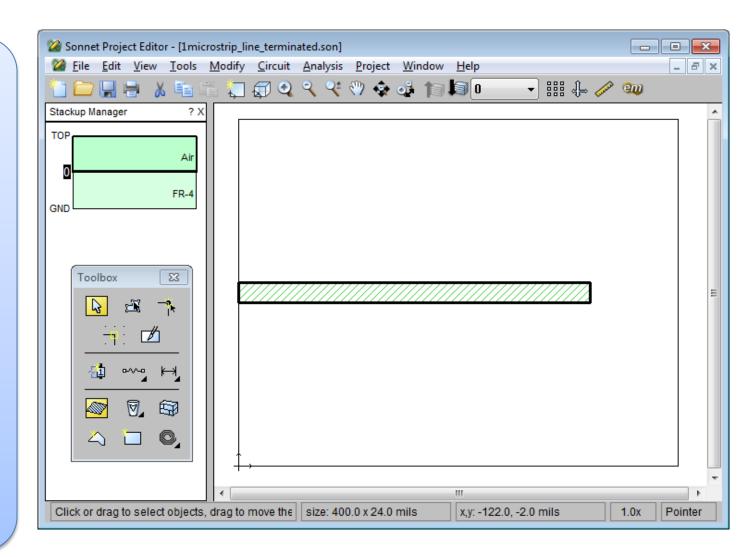

#### **Tutorial SONNET- Completando a linha Microstrip**

Para posicionar o traço mais precisamente, podemos selecioná-lo e em seguida usar o comando do menu Modify -> Center -> **Vertically. Podemos** também usar o teclado e digitar "@" e em seguida a coordenada x, y para um movimento relativo. No entanto. outra maneira de mover uma grade de um polígono em um momento é usar o comando de teclado Shift seta para cima, Shift seta para a esquerda, etc.

O objetivo é ter o traço centrado e também obter a borda esquerda contra a borda do substrato.

#### **Tutorial SONNET- Completando a linha Microstrip**

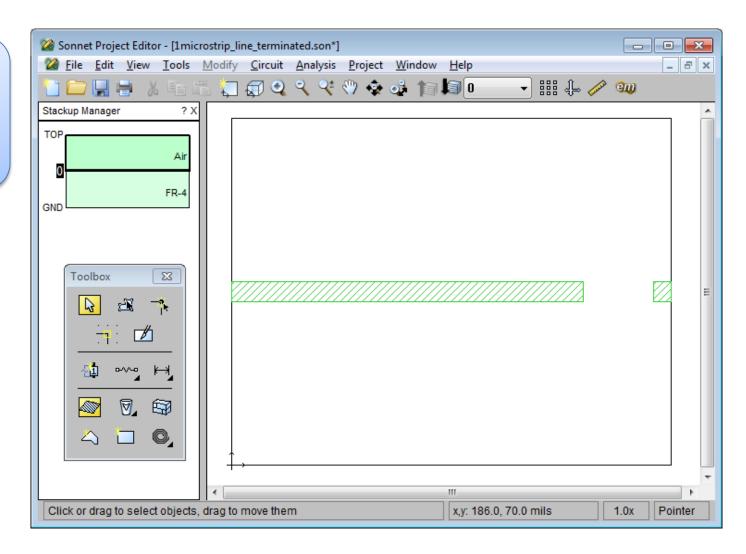

Use etapas semelhantes para adicionar um polígono 20 x 24 mil de forma a posicioná-lo contra a borda direita do substrato

#### **Tutorial SONNET- Completando a linha Microstrip**

#### **Tutorial SONNET- Completando a linha Microstrip**

Use os comando do menu Tools -> Add Port para adicionar uma porta para a borda esquerda do traço. Esta porta vai se comportar como uma porta BoxWall. A porta está inserido em uma infinitamente pequena folga entre a borda do traco e a análise boxwall. O terminal positivo da fonte de porta conectase à extremidade do traco e o terminal negativo para o boxwall. Essa configuração faz com que as portas de análise boxwalls e, potencialmente, a caixa de cobre para estar no caminho da corrente de retorno e comportar-se como um terra.

#### **Tutorial SONNET- Completando a linha Microstrip**

Para que a exibição

Stackup Manager seja

mais completa, podemos

clicar com o botão

direito sobre ele e

selecione Auto Create

Tech Layers. Isto irá

colocar uma Tech Layer

na pilha de metal que

criamos.

Technology Layers são semelhantes às camadas que são encontrados em várias ferramentas de layout do circuito e desenho CAD. Eles fornecem um meio para atribuir atributos para todos os polígonos em uma camada.

#### **Tutorial SONNET- Completando a linha Microstrip**

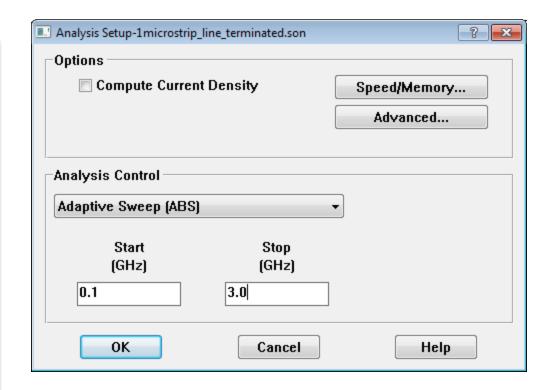

Para concluir a configuração do modelo, é preciso especificar uma varredura de freqüência. Vamos usar a varredura padrão ABS longo de um intervalo de 0,1 a 3,0 GHz.

A varredura ABS utiliza uma técnica de interpolação, onde um número limitado de pontos de freqüência são totalmente analisados e montados em equações. Uma vez que pontos suficientes foram analisados, a resposta de banda larga total é calculada, com bom um intervalo de frequência.

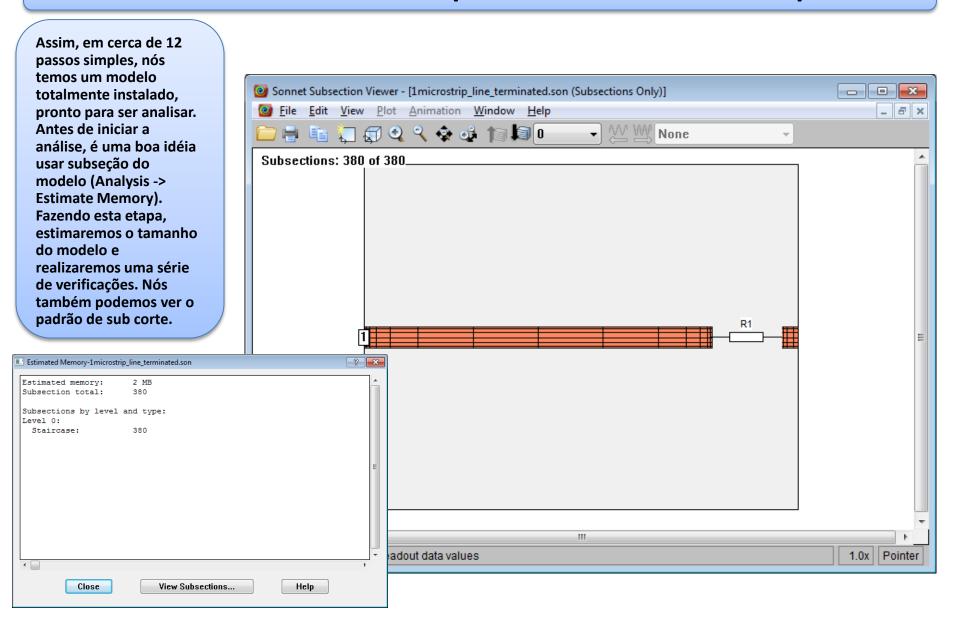

#### **Tutorial SONNET- Completando a linha Microstrip**

#### **Tutorial SONNET- Completando a linha Microstrip**

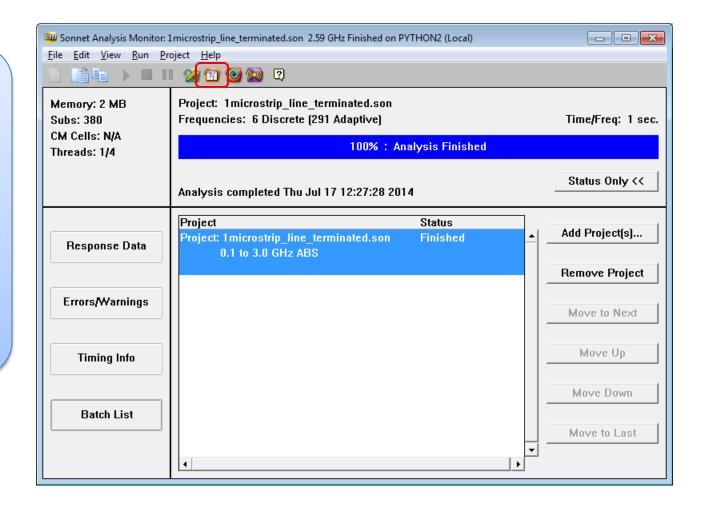

**Use o comando Project** -> Analyze para iniciar o Monitor de Análise e executar a análise. As informações são exibidas enquanto a análise está em execução e claramente é indicado quando esta for concluída. Podemos plotar os dados durante a análise ou quando for concluída. Basta clicar no botão Visualizador de Resposta na barra de ferramentas.

#### **Tutorial SONNET- Completando a linha Microstrip**

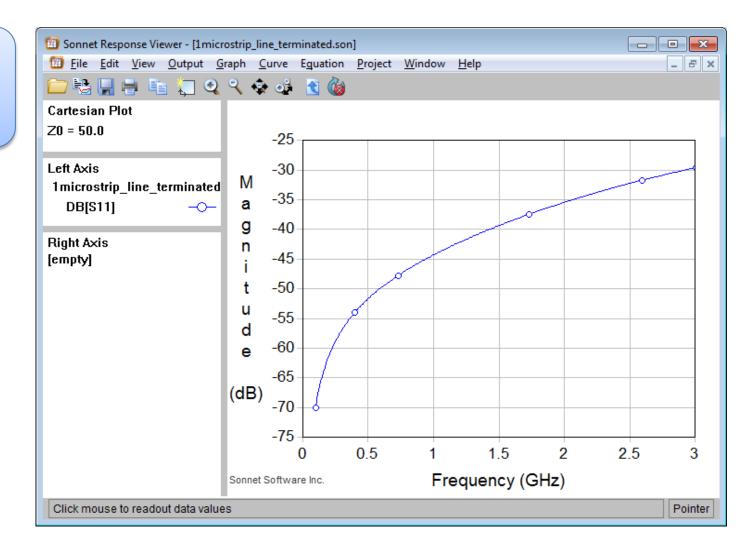

Por padrão, um gráfico cartesiano de S11 em dB, serão plotados no Visualizador de Resposta.

#### **Tutorial SONNET- Completando a linha Microstrip**

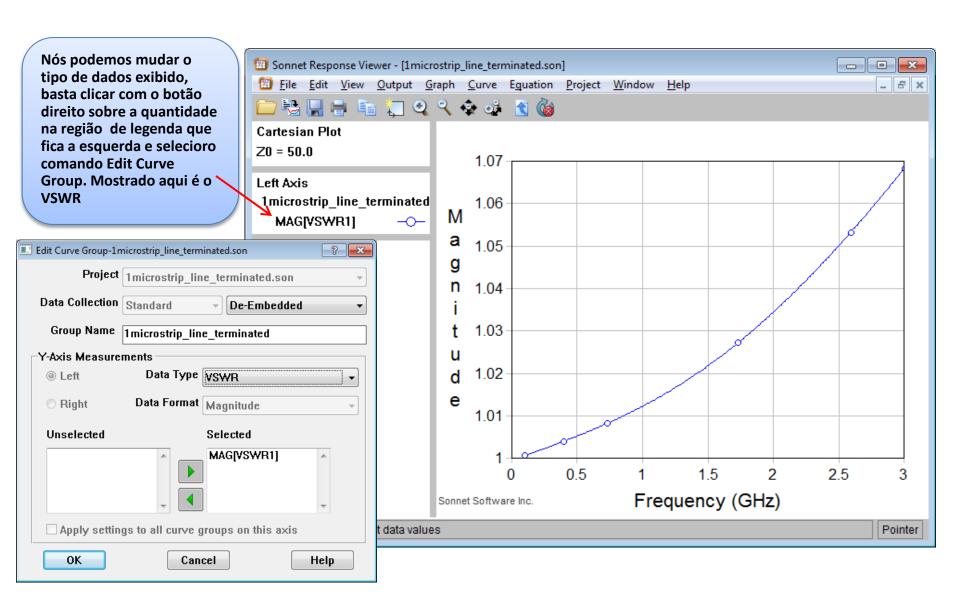

## **Tutorial SONNET- Completando a linha Microstrip**

#### **Tutorial SONNET- Completando a linha Microstrip**

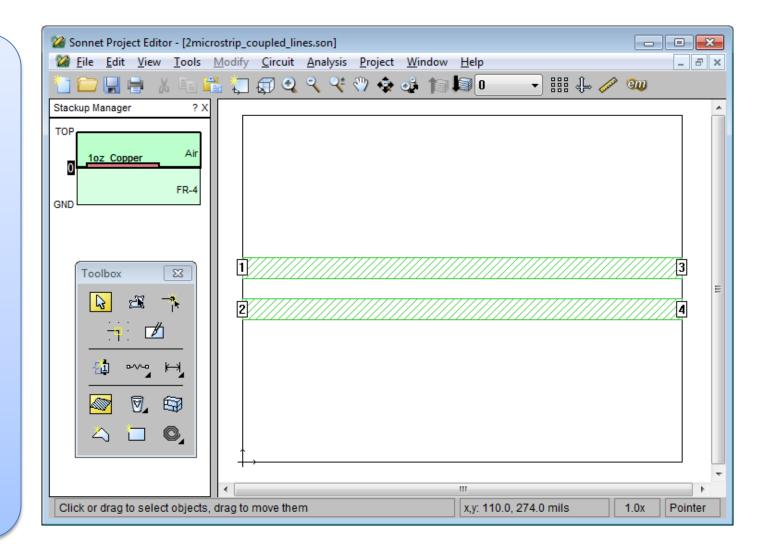

Podemos salvar o modelo anterior com um novo nome e modificá-la rapidamente para criar um modelo de linha acoplado de 4 portas. Abaixo está um resumo das etapas:

- 1) Excluir o resistor e o polígono pequeno.

- 2) Use os comando Tools -> Reshape para esticar o traço do polígono para a parede da direita.

- Use copiar / colar ou Modify -> Move para criar um segundo traço.

- 4) Use Modify -> Center -> Vertically para posicionar os traços.

- 5) Adicionar ou editar as portas conforme necessário.

### **Tutorial SONNET – Linha Microstrip Acoplada**

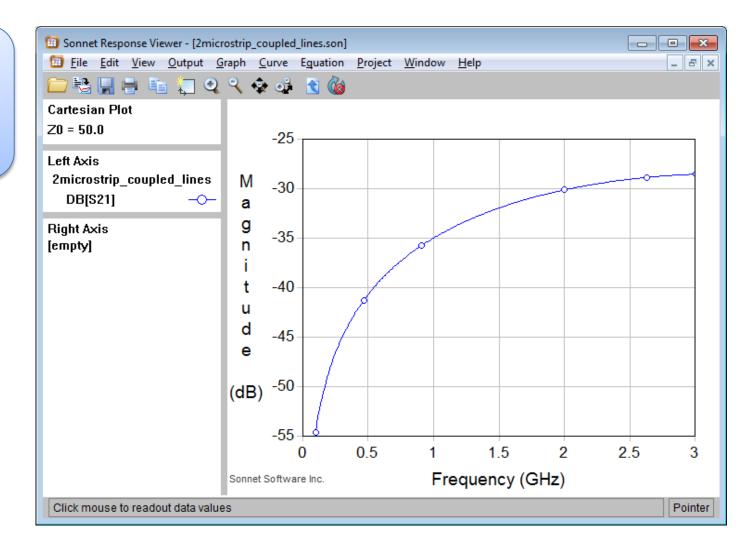

Com este modelo podemos analisar a interferência (Crosstalk) entre os traços. Podemos traçar a Near End Crosstalk (NEXT) usando o dB [S21] Sparâmetro.

#### **Tutorial SONNET – Linha Microstrip Acoplada**

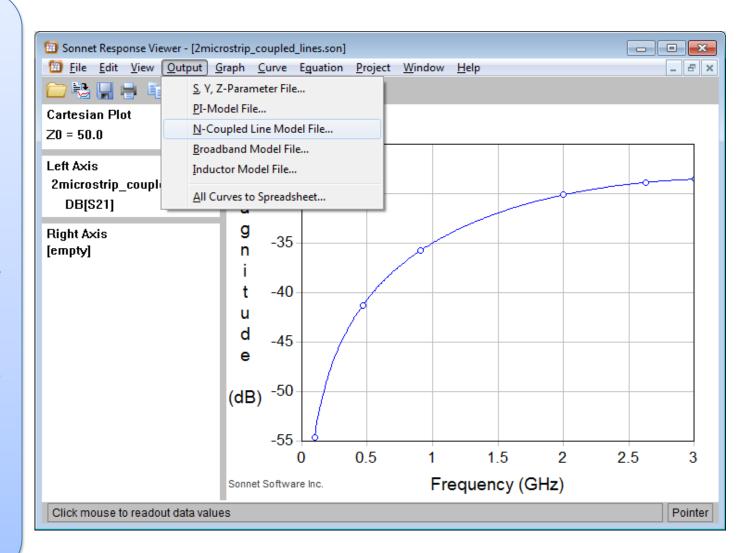

A partir do Visualizador de resposta, podemos extrair uma série de arquivos de saída que pode ser útil para a análise no domínio do tempo:

S, Y, Z-parameter file - algumas ferramentas no domínio do tempo pode trabalhar diretamente com arquivos S-parameter.

Historicamente, esta abordagem não tem sido eficiente.

<u>Pi-Model file</u> - Este arquivo contém uma série de banda estreita de circuitos equivalentes a modelo Pi. Tipicamente, o circuito é um tanto humanamente significativo para os modelos simples.

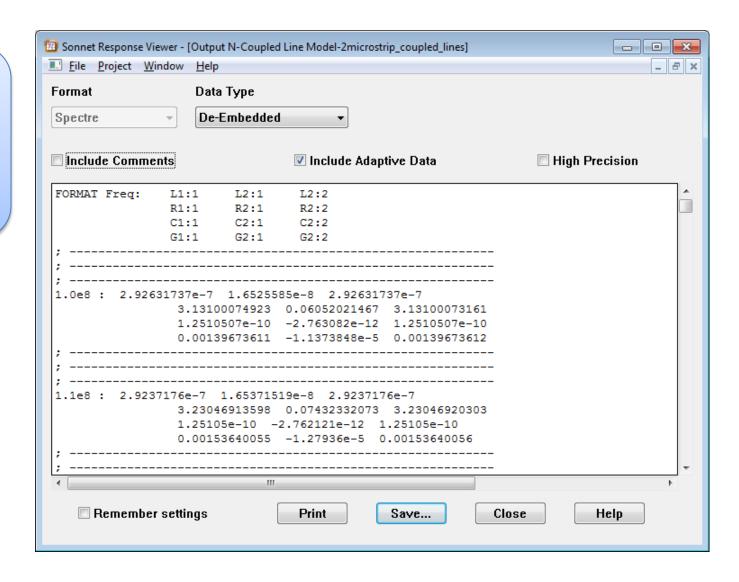

N-Coupled Line file - Essa extração é útil na criação de matrizes RLGC para modelos de linhas de transmissão. Este arquivo pode então ser associado a um elemento de linha de transmissão em SPICE ou ferramenta semelhante.

Broadband Model file - Este arquivo contém um único circuito equivalente para toda a varredura de freqüência. Ele contém fontes e o circuito não é humanamente significativo.

Inductor Model file — Há duas topologias fixas disponíveis para a montagem de um indutor Estes são fisicamente circuitos equivalentes de muita importância e podem ser inseridos como diagramas esquemáticos em ferramentas de domínio de tempo.

## **Tutorial SONNET – Linha Microstrip Acoplada**

Com um modelo de linha acoplado, o arquivo de saída de linha N-Acoplados é provavelmente o mais útil.

Podemos ver o formato e as matrizes RLGC para as linhas de transmissão acopladas.

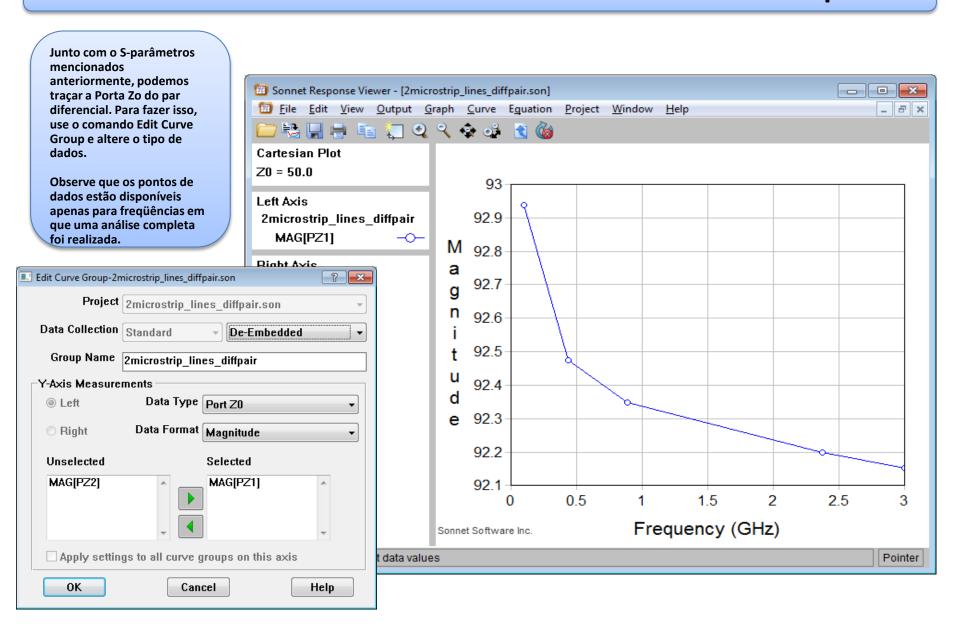

#### **Tutorial SONNET – Par diferencial de Linhas Microstrip**

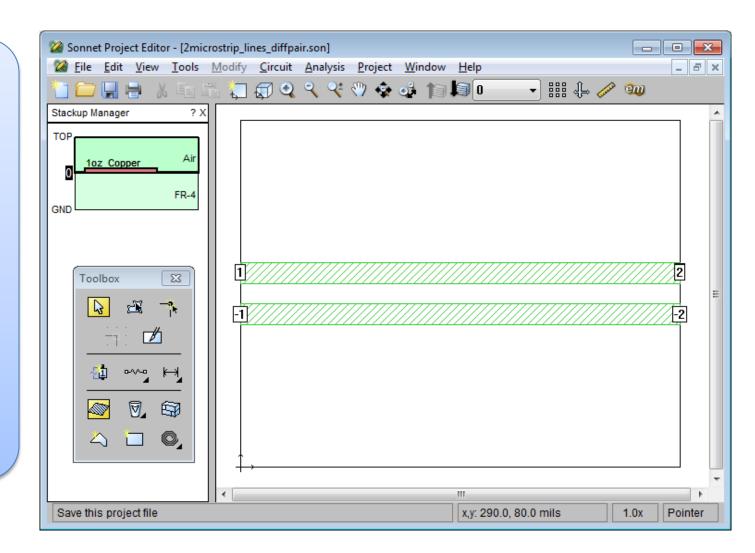

Muitos circuitos digitais usam linhas de sinais diferenciais em vez de linhas de terminação única. Podemos trabalhar com pares diferenciais em Sonnet, simplesmente editando os números das portas e criando +/- pares de porta.

Aqui, nós salvamos o modelo anterior com um novo nome e configuramos como um par diferencial.

Para alguns dados adicionais, a caixa "Compute Current Density" foi verificada sob a caixa de diálogo Analysis Setup

#### **Tutorial SONNET – Par diferencial de Linhas Microstrip**

#### **Tutorial SONNET – Par diferencial de Linhas Microstrip**

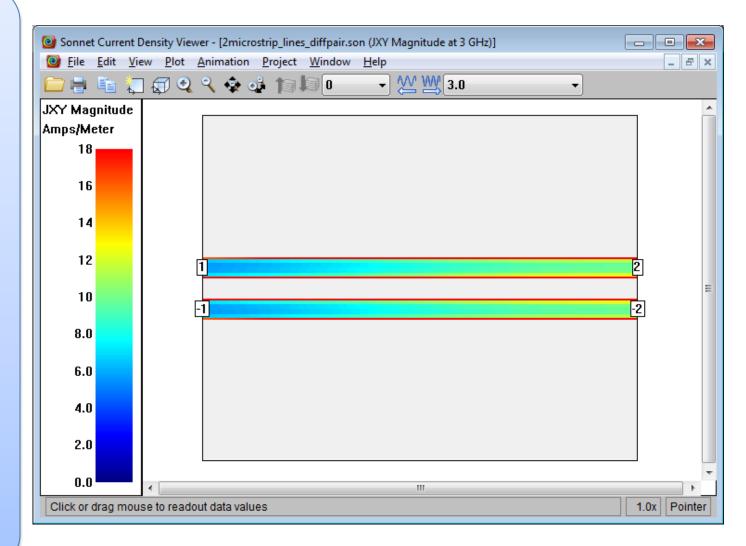

Junto com os dados no domínio da freqüência, o Sonnet solver também pode calcular a densidade de corrente. Você pode plotar esses dados usando o comando Project -> View Current na janela Project Editor.

A densidade de corrente para o par diferencial é mostrada aqui a 3 GHz. Existe alta densidade de corrente sobre as bordas de rastreio, o que é normal para os circuitos de alta frequência. Existe também, geralmente mais baixa, densidade de corrente no lado esquerdo dos traços do que no lado direito. Isto é causado pela incompatibilidade entre o valor par diferencial Zo (92,1 Ohms) e as terminações de porta (50 ohms). Este é o efeito de onda estacionária.

#### Modelo Eletromagnético de linhas de transmissão utilizando Sonnet

#### Concluões de Sonnet como uma ferramenta de Simulação de Integridade de Sinais(SI) Digitais

## Há uma série de aplicações de integridade de sinais que podem ser modelados e simulados em Sonnet. Alguns dos mais úteis são:

- 1. Computar Zo para stackups e geometrias incomuns Muitos projetos de design de PCI usam vários materiais com diferentes valores de Er. Ele também pode conter alguma assimetria na colocação do traço no stackup. Sonnet permite ao usuário calcular o valor de Zo.

- 2. Study various transmission line circuits with both single ended and differential excitation/termination. Estudar vários circuitos de linhas de transmissão com ambos single ended e com excitação / terminação diferenciado.

- 3. Estudar o efeito de vias de multicamadas no trajeto do sinal.

- 4. Estudar crosstalk entre linhas de transmissão.

- 5. Estudar a influência de materiais laminados anisotrópicos e rugosidade de metal de folhas de cobre sobre o percurso do sinal.

- 6. Você pode usar SONNET como uma ferramenta autônoma onde você cria a geometria e a camada stackup diretamente na interface do Sonnet Project Editor interface. Você também pode trabalhar no Microwave Office framework e traduzir um layout existente em Sonnet. Ambos os métodos são bastante úteis. Sonnet também tem boas interfaces dentro da Agilent ADS e Cadence Virtuoso. Sonnet também lê e grava arquivos GDSII e DXF

- 7. Sonnet contém seu próprio visualizador de resposta em que você pode traçar S, Y, Z-parâmetros, Zin, e outras quantidades no domínio da frequência. Sonnet também calcula o valor eficaz de Zo e Er em completa análise de frequências e estas quantidades também podem ser plotados.

- 8. Outra característica é a capacidade de equação no Response Viewer . Há equações internas em que o usuário pode definir seu / sua própria equação. Um exemplo das equações embutidas é o Group Delay.

- 9. Sonnet pode calcular a densidade de corrente em um circuito e caminhos de terra ilustrado

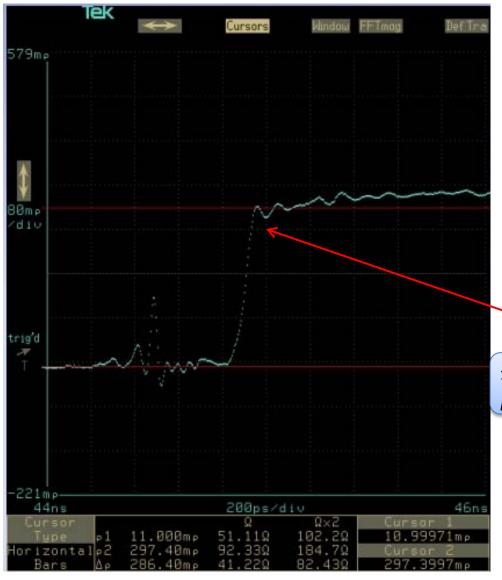

#### Ferramenta de verificação SI- Reflectometria no domínio do tempo (TDR) 1

Reflectometria no domínio do tempo (TDR) mede a resposta refletida de um circuito para um pulso aplicado, para um impedância de sistema definida.

Padrões TDR são normalmente usados para detectar um curto-circuito ou um circuito aberto, testar adequada impedância de terminação e caracterizar descontinuidades de interconexão.

Na avaliação do TDR como um instrumento de diagnóstico de sinal digital, a fonte é um rápido, normalmente <= 40ps, gerador de degrau de voltagem. O conteúdo da frequência do degrau depende do tempo de subida do pulso

Esta medição TDR ilustra o sinal refletido visto por uma fonte de pulso de 50 Ohm em uma terminação de 100 Ohm. Há um degrau no local da terminação incompatível porque ela afasta-se da impedância do sistema de 50 Ohm.

<sup>1</sup> Hall, Hall, and McCall, High-Speed Digital System Design, John Wiley & Sons Inc., 2000: 284 - 303

$$\rho = \frac{V_{reflected}}{V_{incident}} = \frac{Z_{load} - Z_0}{Z_{load} + Z_0}$$

$$Z_{DUT} = Z_0 \cdot \frac{1+\rho}{1-\rho}$$

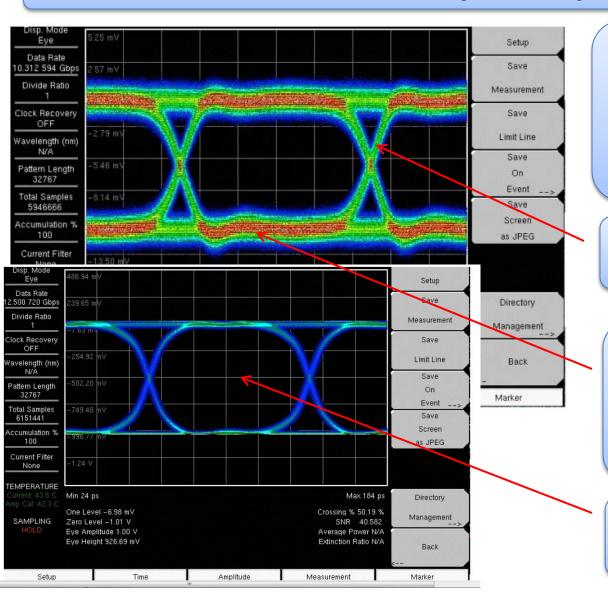

#### Ferramenta de verificação SI- Eye Diagram Mask

O Eye Diagram Mask é uma medição do enlace digital global no domínio do tempo. Muitas sequência de bits são sobrepostas criando série de padrões "eye". Muito pode ser aprendido sobre as características do caminho com esse digrama.

Esse teste é tipicamente usado para verificar links de comunicação longos (óticos e sem fio), mas agora é usado também em novos procidimentos de testes de padrões de links digitais seriais.

Essa medida no diagrama exibe JITTER que aparece como um erro de desalinhamento de tempo nas bordas de subida e descida.

Essa medida no diagrama exibe também ruído excessivo que aparece como alargamento das bandas de amplitude que os níveis de sinal caem dentro.

Ruído e JITTER fazem com que o padrão EYE fechar e irão causar erros de dados.

Esse diagrama ilustra um link serial com menores ruído e JITTER.

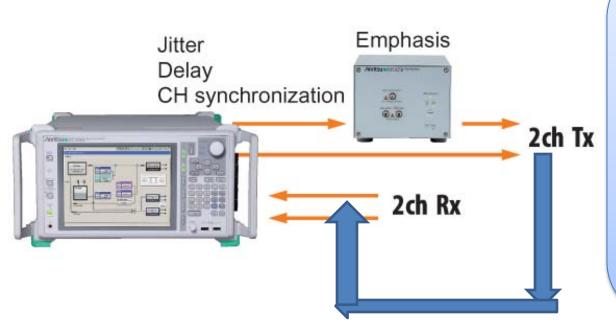

#### Ferramenta de verificação SI – Bit Error Rate Tester (BERT) <sup>3</sup>

Geração de dados BERT é um instrumento de teste de dados comum em produção em série digital. Isso é útil para testar links de comunicação end-to-end. Operadores de telefonia móvel como Verizon e AT&T usam testes BERT diariamente para testar conectividade end-to-end e para assegurar que o link está funcionando corretamente. Para propósitos de desenvolvimento, erros de Jitter, Delays e Sync podem ser injetados e medida a tolerância para esses específicos erros de dados.

Padrões digitais pseudo-aleatórios são gerados e enviados (ver 2ch Tx), o nó remoto é setado para "loopback", e os padrões são casados com o que foi enviado e qualquer erro indicado como "n x 10-6 erros."

**Local/Remote Node in Data Loopback Node**

<sup>3</sup> Johnson and Graham, *High Speed Signal Propagation*, Prentice Hall, 2003: 650

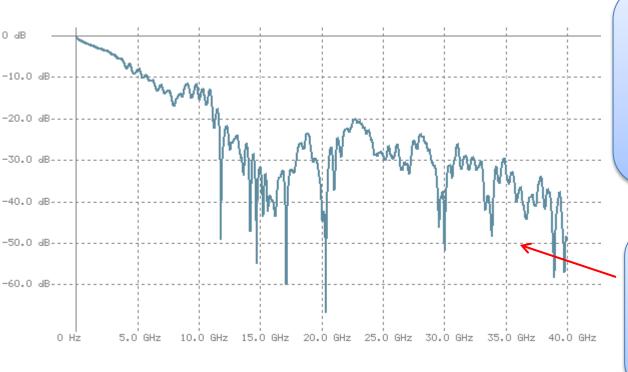

### Ferramentas de Verificação SI - Analisador Vetorial de Redes(VNA)

O Analisador Vetorial de Redes (VNA) mede os parâmetros da rede de um DUT no domínio da frequência. Normalmente os sinais refletidos e transmitidos são medidos por um dispositivos de 2 portas. Essa informação é geralmente mostrada como parâmetros S.

Medições VNA parâmetros S são flexíveis e podem produzir uma riqueza de informações sobre o DUT sobre uma faixar de frequência larga ou estreita.

Essa medição VNA é de S11 com Db. É a medida do sinal refletido na Porta 1. Valores mais negativos indicam menor nível de sinal refletidos e, portanto, um melhor casamento entre a impedância de entrada DUT e o valor da terminação da porta (normalmente 50 Ohms).

$$Z_{\textit{entrada}(\textit{DUT})} = Z_0 \cdot \frac{1 + S_{11}}{1 - S_{11}} \quad S_{11} = \frac{V_{\textit{refletido1}}}{V_{\textit{incidente1}}} = \frac{Z_{\textit{entrada}(\textit{DUT})} - Z_0}{Z_{\textit{entrada}(\textit{DUT})} + Z_0}$$

#### Conclusões do Tutorial

- Há muitos desafios para integração de sinal em projetos digitais de alta velocidade atuais.

- Engenheiros de projetos digitais precisam aproveitar as muitas ferramentas de software disponíveis para ajudar a compreender os problemas de integração de sinal antes de liberar um projeto para a fabricação.

- SONNET fornece capacidades de simulação Digital SI para modelar circuitos planares 3D no domínio da frequência

- Ferramentas de Sistemas Digitais e Metodologia de Sinal, como TDR, VNR, BERT, Eye Diagram, são úteis para práticas de verificação da integridade de sinais e diagnósticos.