Bar vias are vias whose length is significantly longer than their width. Bar vias are identified in the project editor by assigning the Bar meshing fill to a via polygon which uses the Volume loss model. This assignment may also be done automatically, based on a length to width ratio, when using a translator or interface to Sonnet. For more information, please refer to Bar Via Group Simplification.

Since bar vias are only identified in the project editor, the via polygon using the Bar mesh fill is displayed as drawn by the user. The actual metal analyzed by em is calculated during the analysis. Bar via groups are identified and combined, then modeled using the Vertices mesh fill. An example is shown below.

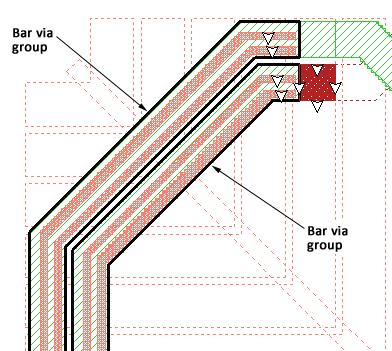

The illustration below shows a section of an inductor which uses bar vias. The bar via polygons are selected and highlighted with a black outline. Note that only part of the via polygons is shown for clarity.

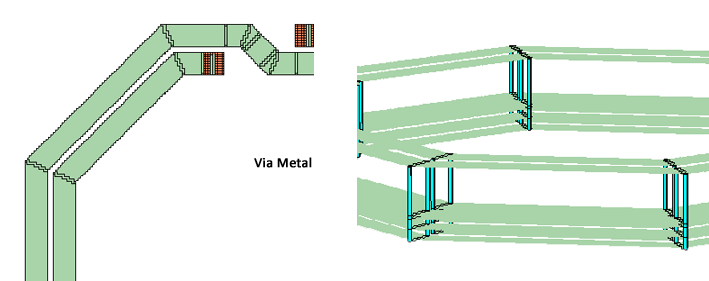

The Sonnet subsectioning automatically places more subsections in critical areas where current density is changing rapidly, but allows larger subsections in less critical areas, where current density is smooth or changing slowly. Therefore, if these vias, placed on the interior of the traces, are not identified as bar vias, the subsectioning requires a much finer resolution, which in turn dramatically increases the memory and time needed for the analysis. The 2D view and 3D view of the subsectioning of the inductor with the vias on the traces, which are not identified as bar vias, is shown below. Planar metal using staircase fill is in orange, planar metal using conformal mesh is green and via metal is blue. Note that even though conformal mesh is applied to the traces, the placement of the vias on the traces forces a staircase fill which is much less efficient for this circuit. The estimated memory to analyze this circuit when not identifying bar vias is 55,994 MB.

Now we will look at the effect identifying the bar vias has on subsectioning and memory requirements. When bar vias are identified, the analysis engine, em, simplifies bar vias to reduce the required memory and processing time. Bar via groups are first identified. In this example, the sets of two bar vias on the same trace make up a bar via group.

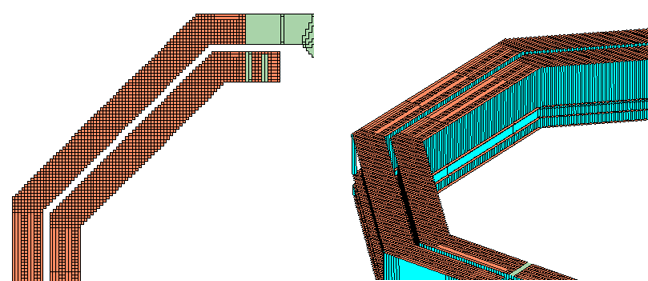

Bar via groups are combined into one simplified via whose edges match the edge of the trace, rather than being on the interior of the trace. This simplified via uses the Vertices meshing fill. The subsectioning of the metal now matches that of traces with no vias as pictured earlier. The 2D and 3D views of the subsectioning of the circuit once the vias have been simplified is shown below; note that via metal only appears at the vertices. In the 3D view, planar metal using staircase fill is depicted in orange, planar metal using conformal mesh is depicted in green and via metal appears in blue. As you can see, the traces can now be modeled using conformal mesh in addition to the savings in metal from simplifying the bar vias. The estimated memory when bar vias are identified is 794 MB, making this a much more manageable analysis.